AMD ujawnia szczegóły najnowszej architektury Zen 5 na konferencji Hot Chips

Na konferencji Hot Chips, AMD przedstawiło szczegółowy wgląd w swoją zupełnie nową architekturę rdzenia Zen 5, która będzie napędzać kolejny etap wysokowydajnych komputerów PC.

szczegółowy wgląd w architekturę rdzenia zen 5

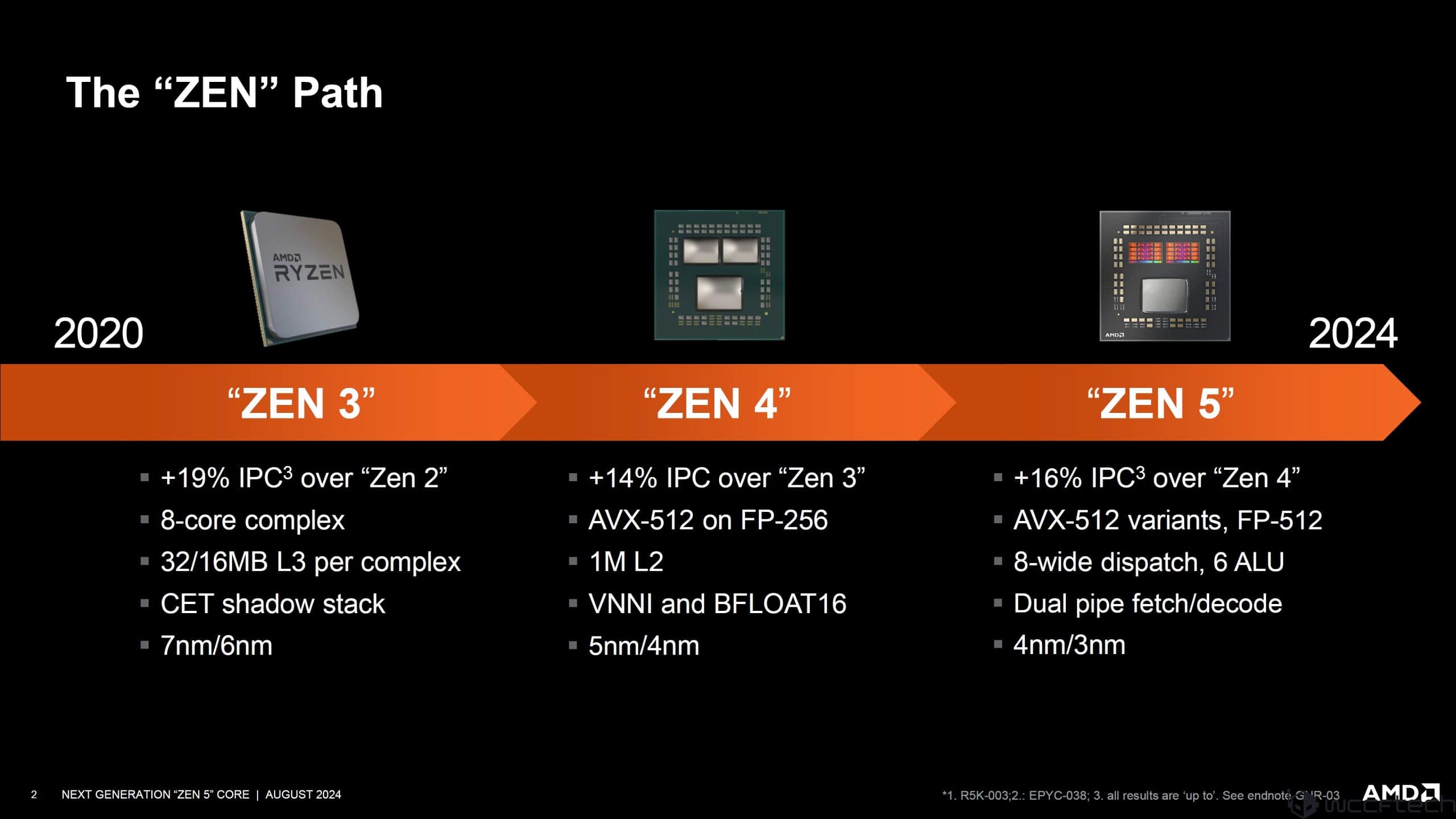

Architektura Zen 1 została wprowadzona przez AMD w 2017 roku, a od tego czasu firma zaprezentowała pięć nowych architektur: Zen+, Zen 2, Zen 3, Zen 4 i teraz Zen 5. W 2021 roku wprowadzono architekturę Zen 4, która przyniosła 14% wzrost IPC, instrukcje AVX-512 (FP-256), podwojenie pamięci podręcznej L2 do 1 MB oraz wsparcie dla VNNI/BFLOAT16, wszystko z wykorzystaniem technologii procesowych 5nm/4nm.

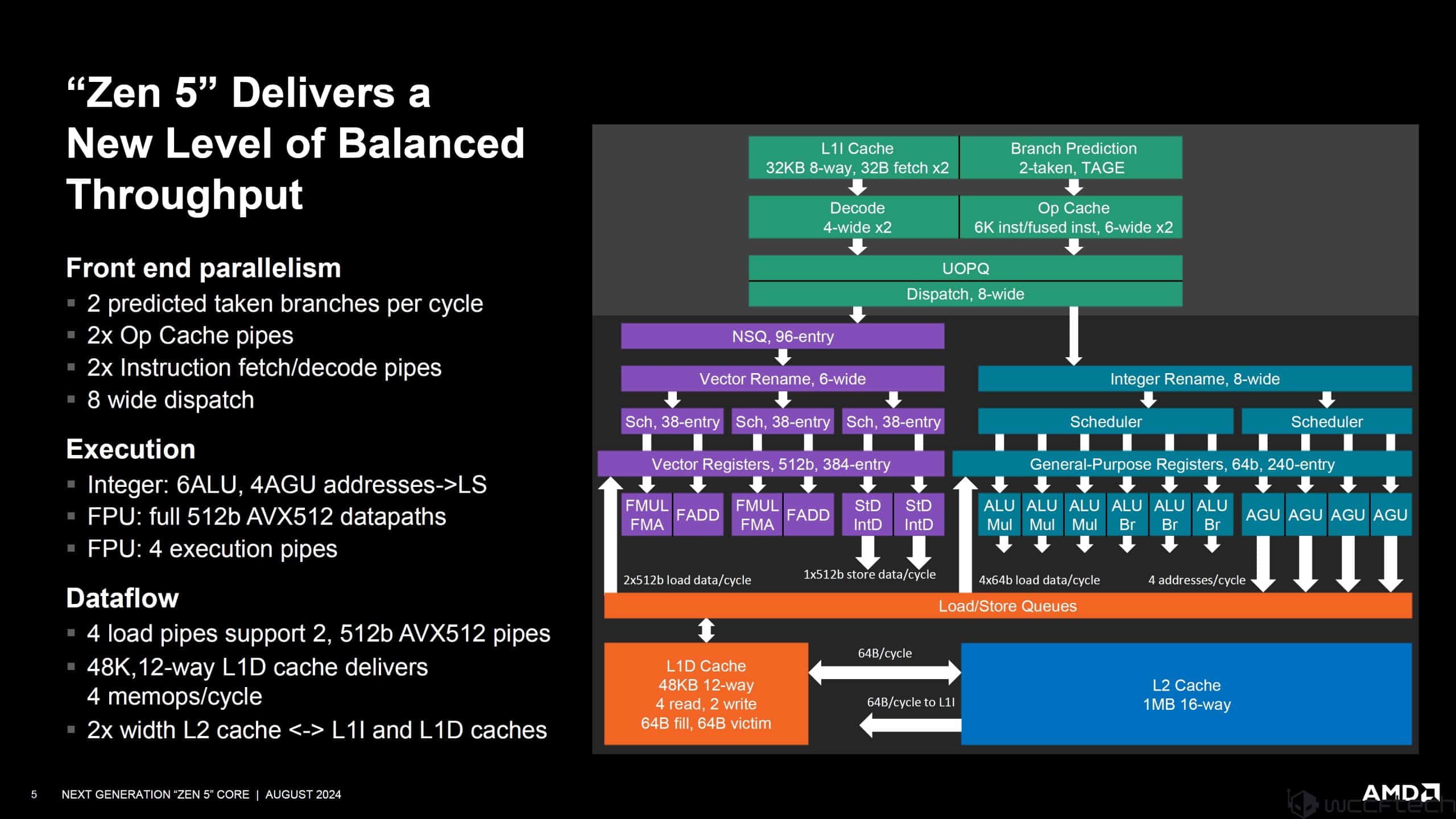

Tegoroczna architektura Zen 5, najnowszy rdzeń o wysokiej wydajności, przynosi 16% wzrost IPC z wariantami AVX-512 i FP-512, 8-szeroką dyspozycję, 6 jednostek ALU, podwójne potoki pobierania/dekodowania oraz wykorzystanie technologii 4nm/3nm. AMD głębiej zagłębia się w pełną architekturę Zen 5 na konferencji Hot Chips.

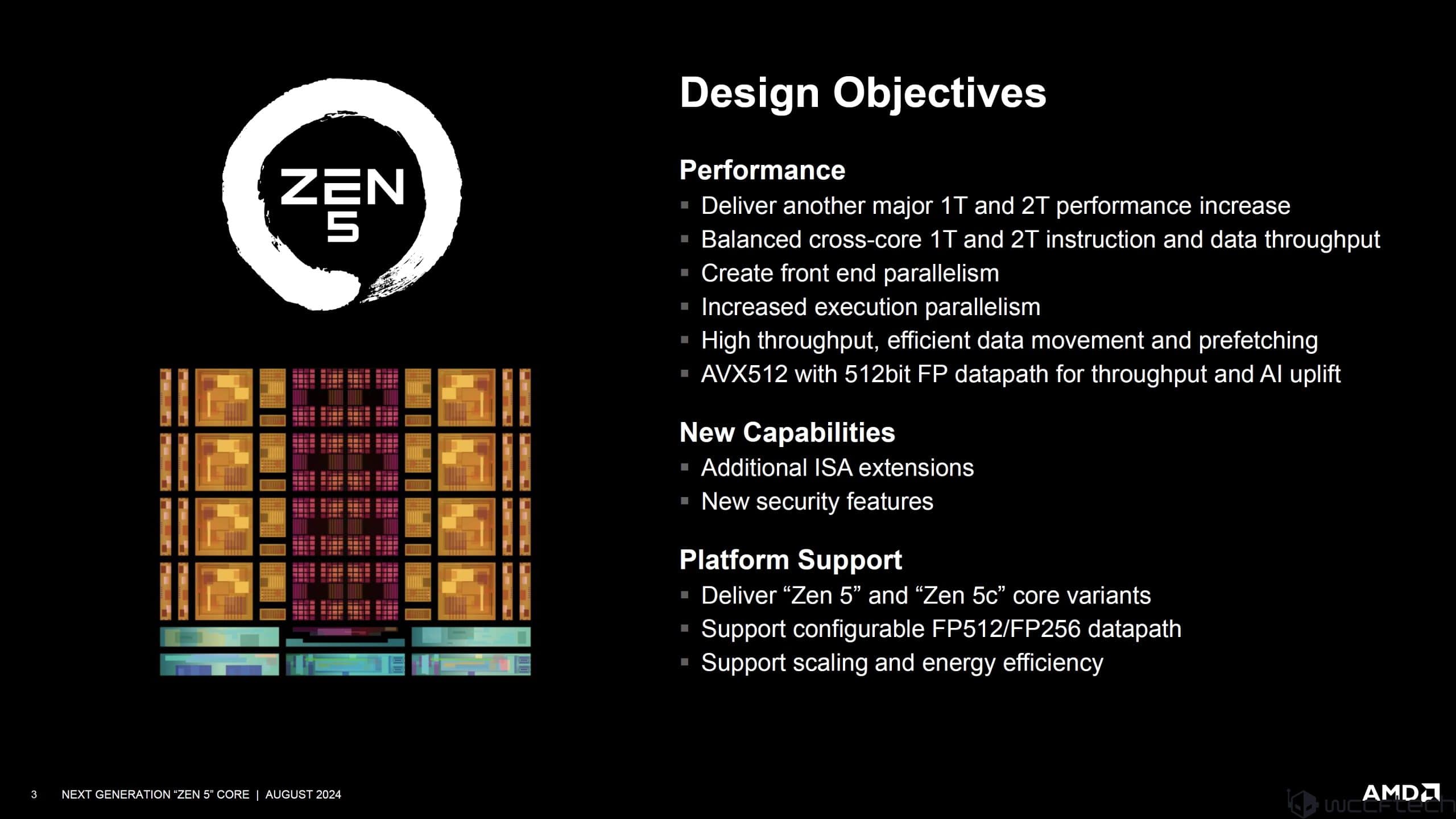

AMD rozpoczyna od podania głównych celów projektowych Zen 5. Jeśli chodzi o wydajność, architektura ma dostarczyć kolejne znaczące zwiększenie wydajności 1T i NT, zrównoważony przepływ komend i danych między rdzeniami, równoległość front-end, zwiększenie równoległości wykonania, wysoki przepływ, wydajne przenoszenie danych i prefetching oraz wsparcie dla ścieżek danych AVX512/FP512 dla przepustowości i podwyższeń AI. Jednocześnie AMD chce dodać nowe funkcje, takie jak dodatkowe rozszerzenia ISA, nowe funkcje bezpieczeństwa oraz rozszerzone wsparcie dla platform.

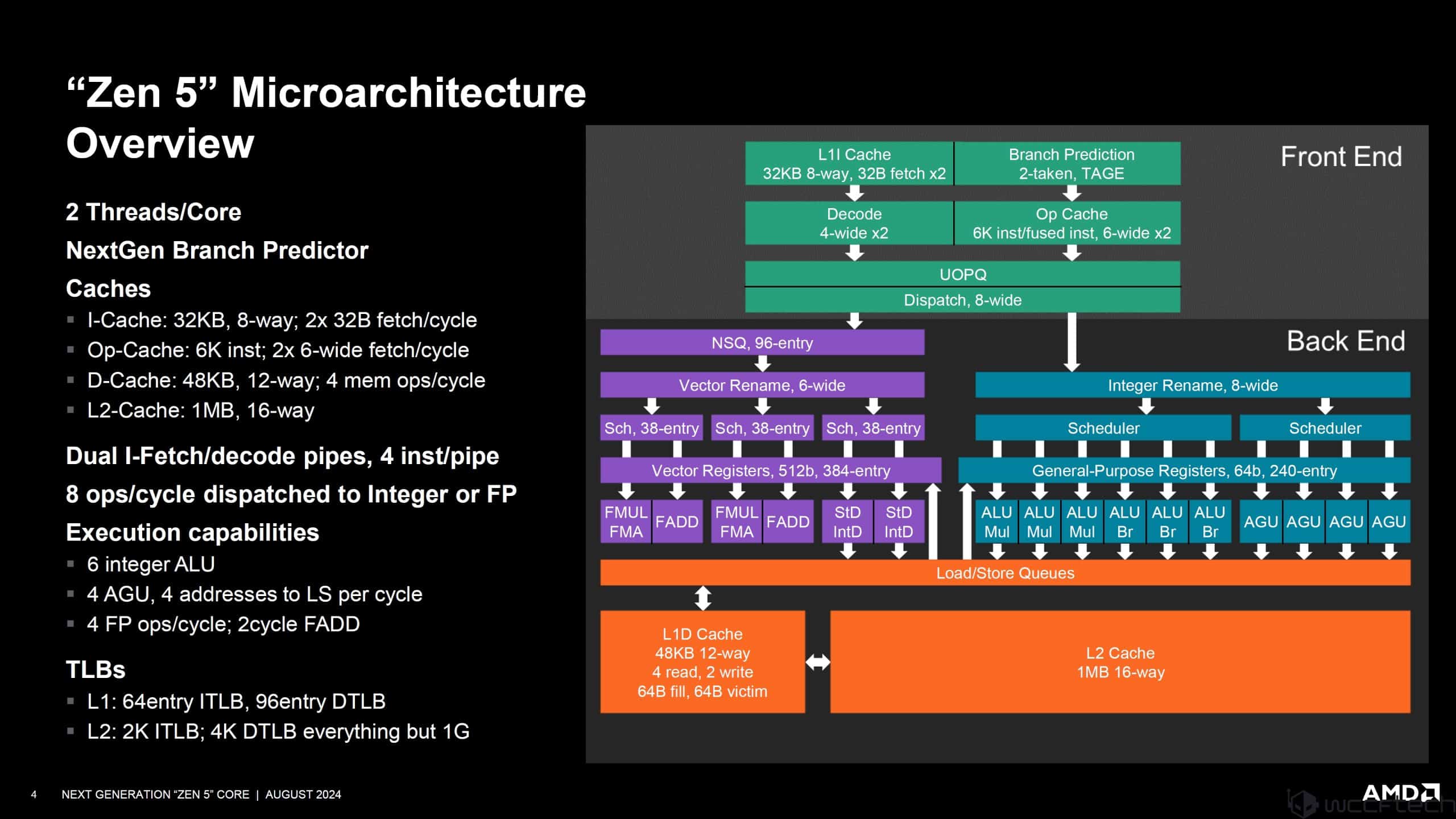

Ogólny przegląd architektury rdzenia Zen 5:

- 2 wątki/rdzeń

- NextGen Branch Predictor

- Pamięci podręczne:

- Pamięć podręczna instrukcji L1: 32KB, 8-way; 2x32B pobieranie/cykl

- Pamięć podręczna operacji L1: 6K instrukcji; 2x 6-szerokie pobieranie/cykl

- Pamięć podręczna danych L1: 48KB, 12-way; 4 operacje pamięci/cykl

- Pamięć podręczna L2: 1MB, 16-way

- Podwójne rury do pobierania/dekodowania, 4 inst/cykl

- 8 operacji/cykl wysyłanych do jednostek całkowitoliczbowych lub FP

Wydajność architektury Zen 5:

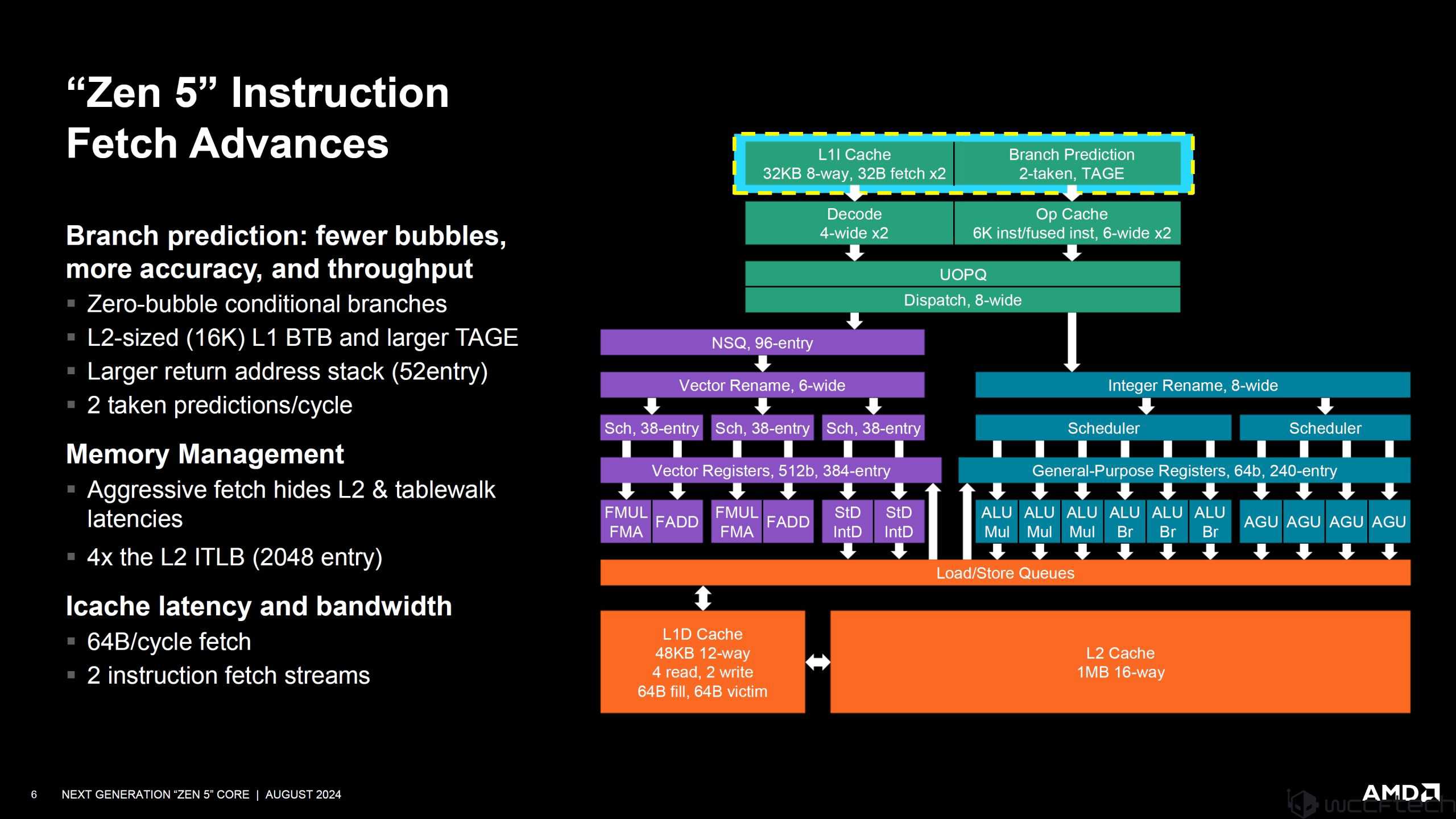

- Przewidywanie rozgałęzień: mniej przerw, większa dokładność i przepustowość

- Zero przerywanych warunkowych gałęzi

- Większy bufor przewidywania przejść (16K) L1 BTB i większa TAGE

- Większy stos adresów zwrotnych (52 wpisy)

- 2 przewidywania na cykl

Zarządzanie pamięcią:

- Aggressive fetch ukrywa latencje L2 i table walk

- 4x bufor ITLB L2 (2048 wpisów)

Gotowe rozwiązania:

- Ryzen 9000 “Granite Ridge” Desktop CPUs

- Ryzen AI 300 “Strix” Laptop CPUs

- 5th Gen EPYC “Turin” Data Center CPUs

AMD dopiero zaczęło z Zen 5, dlatego możemy spodziewać się jeszcze więcej produktów w przyszłości, gdy firma będzie dopracowywać architekturę dla komputerów PC i serwerów.